toofastforyahuh

n00b

- Joined

- Jun 14, 2012

- Posts

- 10

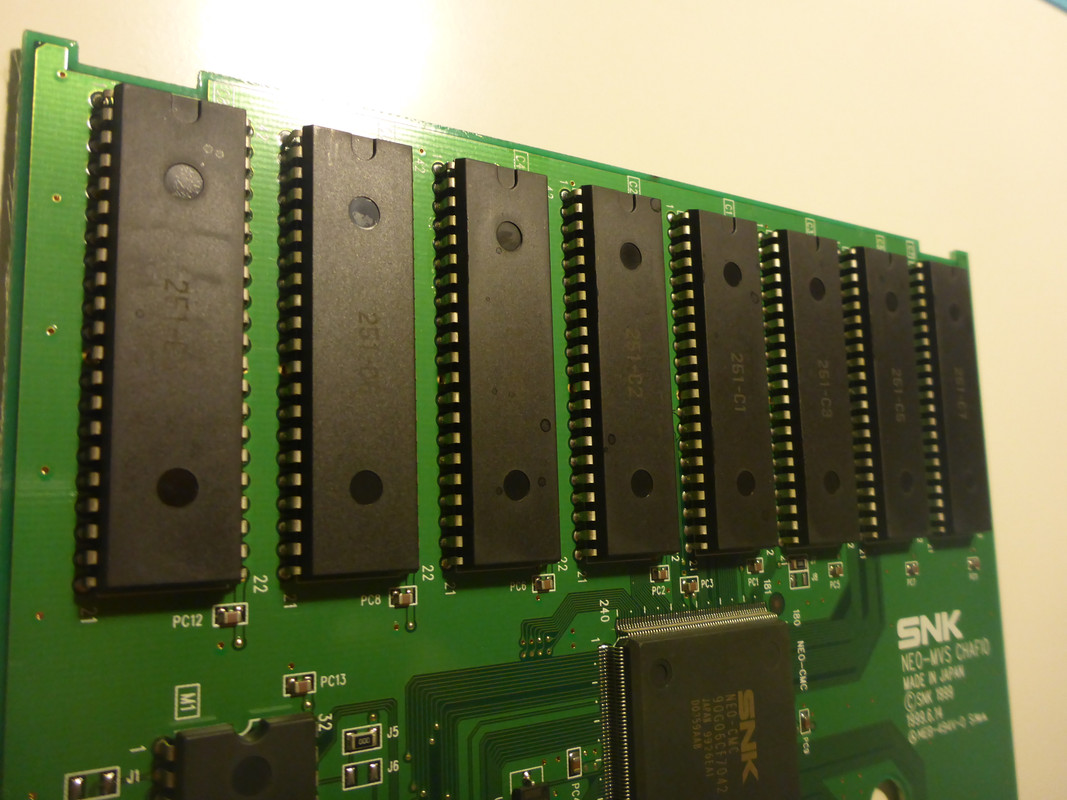

Yet another problematic CHAFIO scrambled graphics thread. I've seen these previous Metal Slug 3 and Nightmare in the Dark threads.

http://www.neo-geo.com/forums/showt...k-Glitchy-Scrambled-Graphics&highlight=CHAFIO

http://www.neo-geo.com/forums/showthread.php?267831-Problem-with-Metal-Slug-3-MVS&highlight=CHAFIO

My CHAFIO scrambled graphics misadventure started 5 years ago with a trip to Japan. Found a wonderful deal on a very much used MVS Metal Slug 3 in Akihabara. It was not super pretty and had obviously been opened before, but it was cheap, a game I wanted, and a great souvenir. Here's the condensed story of the aftermath:

1. Cleaned it thoroughly, but it had corrupt graphics from day 1. Cleaned it again, and the graphics corruption went away ---- for only a month.

2. Opened it up. Cleaned CHAFIO again.

No luck. Goofed around with bare boards in the MVS (being of course dilligent about board order and orientation!) Noticed mechanical pressure on one of the C ROMs cleared it up briefly, so I assumed there was a bad solder joint. Reflowed that particular C ROM, and the game was perfect! For a month.

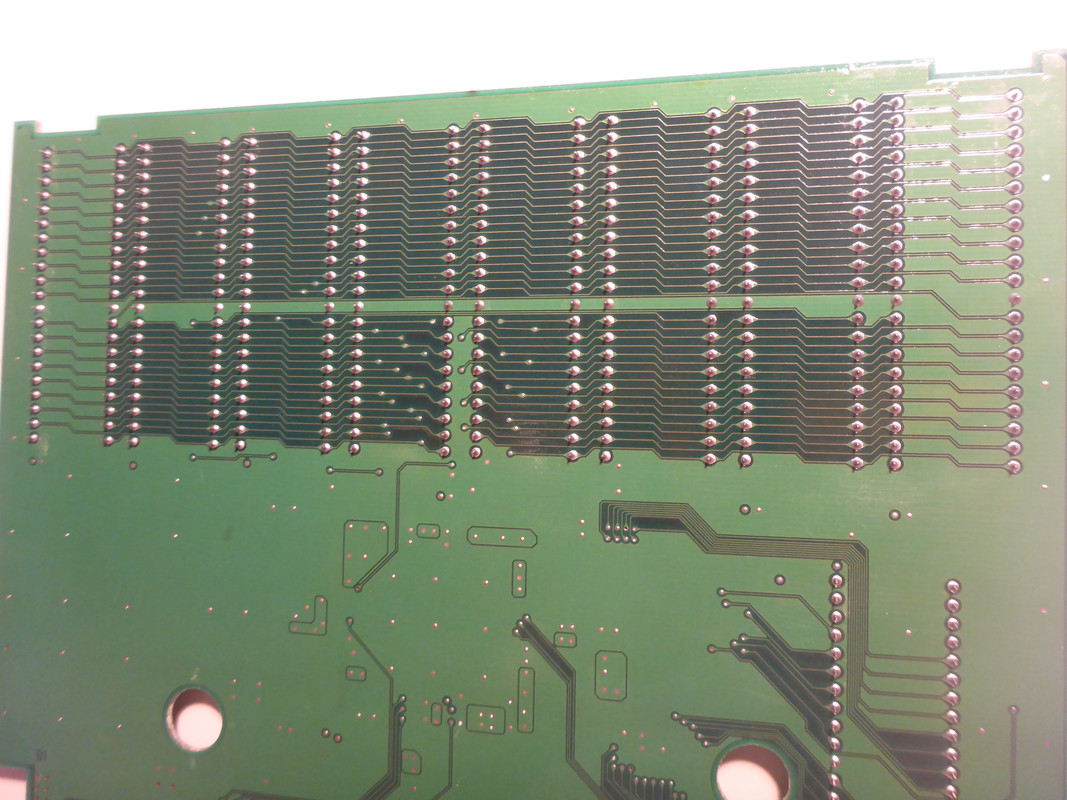

3. Opened it up again and this time reflowed all 8 C-ROMs. Actually tried to remove one and test it with my Batronix Batego 2, but I could never get more than half of the data out because there's no 64 megabit chip setting in the Batronix recognized chip repertoire (32 megabit was the closest I could get). In any event, the 32 megabits it read out seemed OK.

After replacing and reflowing all 8 C-ROMs, the game played perfectly. This time for 3 months.

4. Today I decided to work on it again, this time removing and testing M1 EPROM, which I should have done in the first place because it's only 4-megabit. However, the M1 EPROM tests fine, and replacing it with new solder made no difference.

5. I have also done continuity tests across all 8 C-ROMs (address, data, etc.) and they SEEM fine, at least on my workbench. Similarly did my best to continuity check between the NEO-CMC and C-ROM and M1-EPROM, as well as between the cartridge pins and surface mount resistors and NEO-CMC. This also seems OK on my workbench. That said, every now and then applying mechanical pressure (i.e. pull out the CHAFIO board, pinch something, reinsert it and test again) can change the corruption pattern seen, but I cannot identify a particular area causing the problem.

So obviously anything faulty in the entire CHAFIO board can cause highly visible corruption because every component in the board is used for descrambling the tile data. I think I've ruled out M1 for now. And although I cannot prove it, I'm inclined to believe the C-ROM silicon is OK (or else it never would have worked cleanly at all).

But between C-ROM silicon and NEO-CMC silicon we have:

a) wire-bond to DIP package lead frame

b) board traces

c) board vias

d) wire-bond from NEO-CMC QFP lead frame to silicon.

And there are also

e) surface mount decoupling capacitors and resistors. Certainly a bad solder joint on a decoupling cap could cause havoc on this board by injecting noise.

Ideas?

One thought is to reflow the entire PCB, in case any surface-mount solder is bad. As someone pointed out, there's a huge ground plane acting as heat sink on this board. I wonder how good the solder was out of the factory?

Not every via has a solder plug either. Shouldn't be a problem unless a via is broken.

Another thought is to try to make it worse --- use freeze spray to try to isolate bad joints. Still not an easy task.

Has anyone ever scoped the power rails near the NEO-CMC to see if they are noisy? I wasn't sure if 4 decoupling caps (one on each side) is enough for the CMC?

http://www.neo-geo.com/forums/showt...k-Glitchy-Scrambled-Graphics&highlight=CHAFIO

http://www.neo-geo.com/forums/showthread.php?267831-Problem-with-Metal-Slug-3-MVS&highlight=CHAFIO

My CHAFIO scrambled graphics misadventure started 5 years ago with a trip to Japan. Found a wonderful deal on a very much used MVS Metal Slug 3 in Akihabara. It was not super pretty and had obviously been opened before, but it was cheap, a game I wanted, and a great souvenir. Here's the condensed story of the aftermath:

1. Cleaned it thoroughly, but it had corrupt graphics from day 1. Cleaned it again, and the graphics corruption went away ---- for only a month.

2. Opened it up. Cleaned CHAFIO again.

No luck. Goofed around with bare boards in the MVS (being of course dilligent about board order and orientation!) Noticed mechanical pressure on one of the C ROMs cleared it up briefly, so I assumed there was a bad solder joint. Reflowed that particular C ROM, and the game was perfect! For a month.

3. Opened it up again and this time reflowed all 8 C-ROMs. Actually tried to remove one and test it with my Batronix Batego 2, but I could never get more than half of the data out because there's no 64 megabit chip setting in the Batronix recognized chip repertoire (32 megabit was the closest I could get). In any event, the 32 megabits it read out seemed OK.

After replacing and reflowing all 8 C-ROMs, the game played perfectly. This time for 3 months.

4. Today I decided to work on it again, this time removing and testing M1 EPROM, which I should have done in the first place because it's only 4-megabit. However, the M1 EPROM tests fine, and replacing it with new solder made no difference.

5. I have also done continuity tests across all 8 C-ROMs (address, data, etc.) and they SEEM fine, at least on my workbench. Similarly did my best to continuity check between the NEO-CMC and C-ROM and M1-EPROM, as well as between the cartridge pins and surface mount resistors and NEO-CMC. This also seems OK on my workbench. That said, every now and then applying mechanical pressure (i.e. pull out the CHAFIO board, pinch something, reinsert it and test again) can change the corruption pattern seen, but I cannot identify a particular area causing the problem.

So obviously anything faulty in the entire CHAFIO board can cause highly visible corruption because every component in the board is used for descrambling the tile data. I think I've ruled out M1 for now. And although I cannot prove it, I'm inclined to believe the C-ROM silicon is OK (or else it never would have worked cleanly at all).

But between C-ROM silicon and NEO-CMC silicon we have:

a) wire-bond to DIP package lead frame

b) board traces

c) board vias

d) wire-bond from NEO-CMC QFP lead frame to silicon.

And there are also

e) surface mount decoupling capacitors and resistors. Certainly a bad solder joint on a decoupling cap could cause havoc on this board by injecting noise.

Ideas?

One thought is to reflow the entire PCB, in case any surface-mount solder is bad. As someone pointed out, there's a huge ground plane acting as heat sink on this board. I wonder how good the solder was out of the factory?

Not every via has a solder plug either. Shouldn't be a problem unless a via is broken.

Another thought is to try to make it worse --- use freeze spray to try to isolate bad joints. Still not an easy task.

Has anyone ever scoped the power rails near the NEO-CMC to see if they are noisy? I wasn't sure if 4 decoupling caps (one on each side) is enough for the CMC?