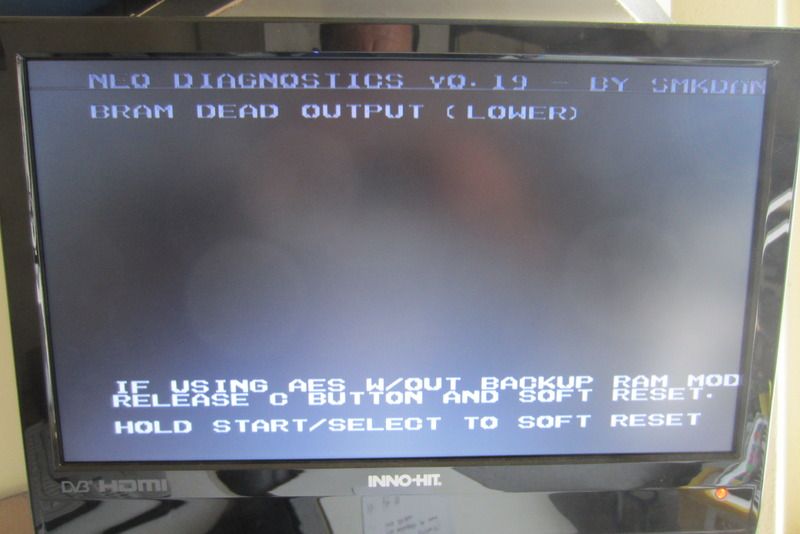

The problem is, there will be a point in time when those logic levels will change in order that access to the BRAM is enabled or disabled, depending on what the processor wants access to. What I suspect is happening (I could be wrong), is that possibly the Neo-C1 is enabling (or not) the BRAM at the wrong time. ie. The outputs there on that 74HC32 all look high at the point you are checking with the logic probe, but they should actually go low at some point, and maybe they aren't. That's where a logic probe doesn't help - it's showing that the HC32 seems OK, but the input to the HC32 might not be correct.

There are limited things at play here, consider it like this:-

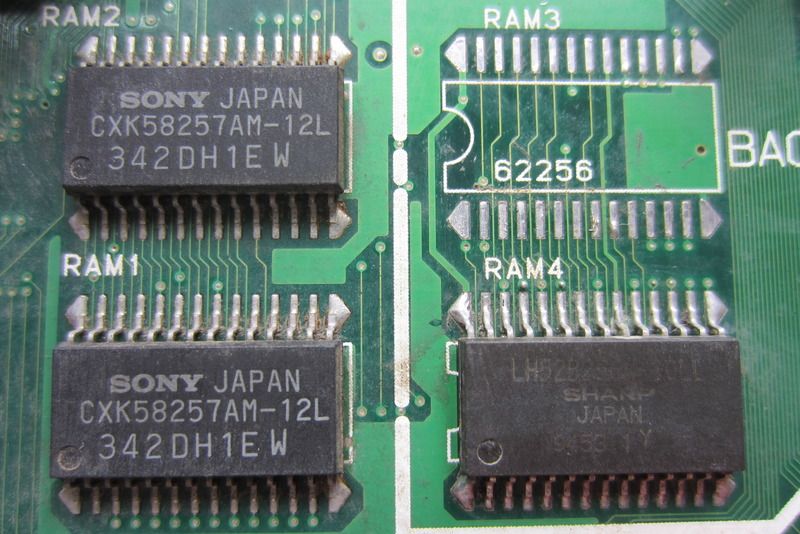

1) BRAM and WRAM address and data lines are connected to the 68K CPU (you've checked those and apparently all OK, so you can rule that out).

2) You've replaced the SRAM, so you can rule that out.

3) You've checked VCC and ground connections to SRAM.

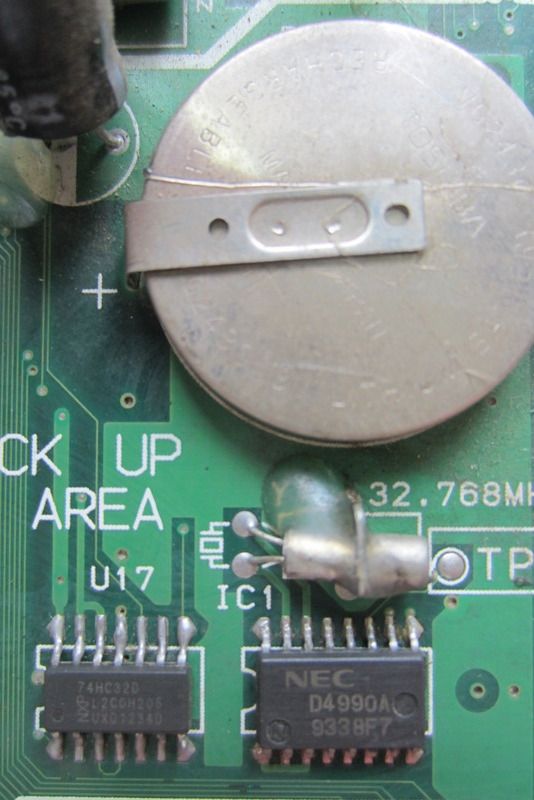

4) Write enable (WE) for the lower and upper BRAM banks goes through the HC32, which you've swapped out.

5) CS and OE look to come from the Neo-C1 (I could be wrong here, hard to read on the diagram)

I think your problem relates to 4 or 5. Either the BRAM is not enabled at the correct time (perhaps no OE or CS - guessing they should be active low), and similarly, maybe if those are OK maybe the WE is not correct, so maybe the chip can be enabled and read, but not written to. If I was to hazard a guess I would suspect the C1, or a bad connection from C1 with relation to OE, CS, or WE.

I guess the other possibility here is something else on the databus is enabled at the same time as the BRAM is accessed (bus conflict) - maybe the WRAM is not disabled when it should be or something?

![IMG_3254[1] (1).JPG](/forums/data/attachments/34/34841-3d9a3fdedbb1d1a3fecf1237df9e015a.jpg)

![IMG_3255[1] (1).JPG](/forums/data/attachments/34/34842-0572248833db3537013fda082fb7e14f.jpg)

![IMG_3256[1].JPG](/forums/data/attachments/34/34843-0766b8448d2505450ea5e766b30dc466.jpg)